下一个时钟上升沿d值为1,那么q就输出1,如此类推。这也d触发器功能,非常非常地简单。 那么这个D触发器在FPGA里面用verilog代码怎么描述呢? 其实也

关于D触发器知识-普通电路,以及常规逻辑门都有一个共厂,那也输出直接依赖于输入,当输入消失时候,输入也跟着不存在了。触发器不同,当它触发

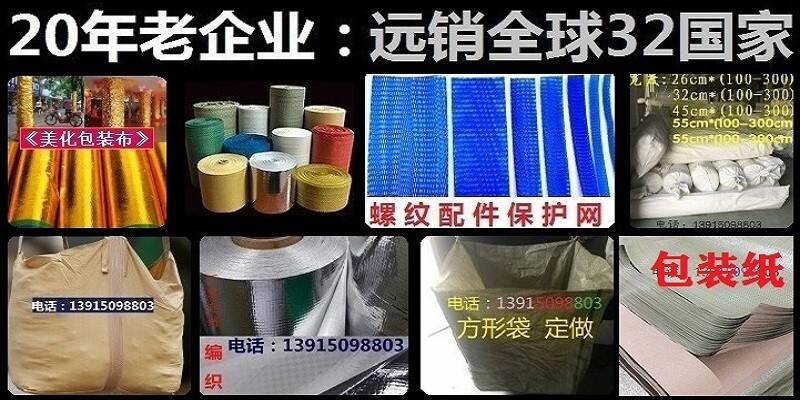

D触发器在FPGA里用得很多,但我经常无法理解D触发器为什么能对数据延迟一个时钟周期(打一拍)。牛皮纸从信号处理角度来谈一下我理解。如发现理解有误,

如图所示,图中排名个触发器D接8个触发器非Q端,这个时序图,整不明白啊,我看法是:当排名个时钟信号高电平来时候,排名个触发器输出状态Q是不

GN74HC74 2.0V-6.0V 2路带置位/复位上升沿触发D型触发器 SOP14/DIP14/TSSOP14GN74HC125 2.0V-6.0V 带三态控制4路缓冲器/线驱动器 SOP14/DIP14